SerDes( Serializer /Deserializer ) 或串行器/解串器是一种集成电路(IC 或芯片)收发器,可将并行数据转换为串行数据,反之亦然。发送器部分是并行到串行转换器,接收器部分是串行到并行转换器。大多数 SerDes 设备支持全双工操作,这意味着数据转换可以同时在两个方向上进行。

SerDes 芯片通过在传输并行数据之前将其转换为串行流,然后在目标点将其转换回并行数据,促进两点之间的数据传输。以这种方式转换数据可减少传输数据所需的数据路径数量以及所需的连接引脚或电线数量。它还解决了传输并行数据带来的其他问题,例如更大的功耗、易受电磁干扰以及时钟时序偏差的可能性。

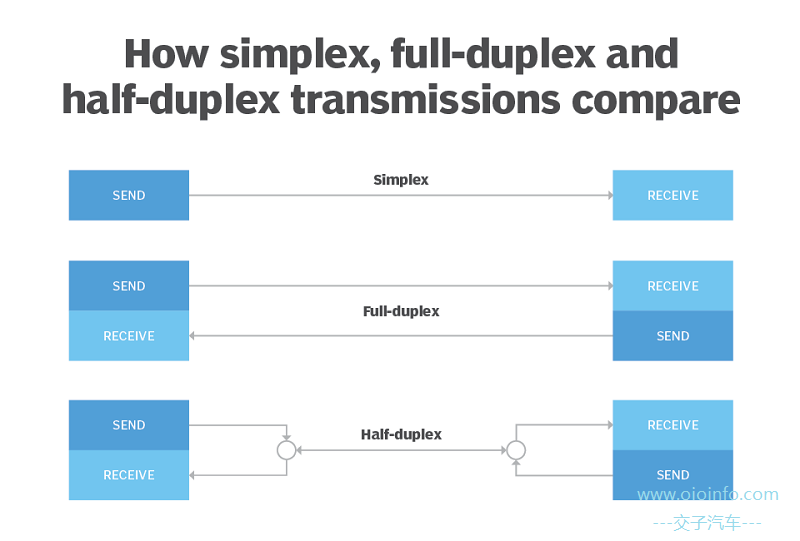

大多数串行器/解串器收发器支持全双工操作,有助于同时在两个方向上进行转换。

SerDes 设计基础

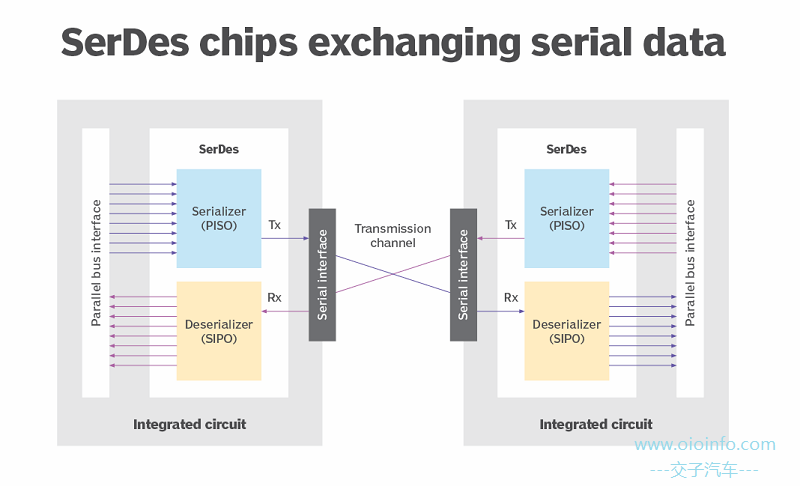

一个 IC 可以容纳多个 SerDes 设备,而一个 SerDes 设备可以容纳多个通道,每个通道处理串行接口的输入和输出流量。尽管 SerDes 设备可能有所不同,但它们通常包含两个功能块:

并行输入串行输出 (PISO)

PISO 是一个并行到串行转换器(串行器)。它从本地系统接收并行数据作为输入,将其转换为串行数据并将其输出为单个数据流,然后通过串行传输通道(如同轴电缆或双绞线电缆)进行传输。在对数据进行序列化时,PISO 使用来自参考时钟的输入作为编码过程的一部分,从而最大限度地减少并行传输中发现的时序问题类型。

串行输入并行输出 (SIPO)

SIPO 是一个串行到并行转换器(解串器)。它接收串行数据作为输入,将其转换为并行数据并将其输出为并行数据流,该数据流通常被发送到连接到集成电路(例如片上系统、现场可编程门阵列或专用集成电路)的并行总线接口。

下图提供了两个 SerDes 芯片通过串行传输通道交换串行数据的概念概述。每个芯片都包括 PISO 串行器和 SIPO 解串器。串行器从并行总线接口接收数据,将其转换为串行数据,并将其流式传输到传输通道。同时,每个 SerDes 上的解串器从另一个 SerDes 接收传入的串行流,将其转换为并行数据流并将其发送到并行总线接口。

该图展示了一对 SerDes 芯片通过串行传输通道交换串行数据。

SerDes 芯片可能还包括编码器、时钟乘法器单元、物理编码子块、时钟和数据恢复单元、输入和输出暂存区或其他组件。

用于序列化和反序列化数据的最重要的组件之一是锁相环 (PLL),它是一种对频率和相位敏感的闭环反馈控制系统。PLL 会根据参考时钟的相位和频率生成串行频率信号。PISO 在序列化并行数据输入时使用 PLL 信号。SIPO 在反序列化数据时也会使用 PLL 作为参考时钟。PLL 可能位于 SerDes 块的内部或外部。此外,每个块可能都有自己的 PLL,或者两个块可能共享同一个 PLL。

SerDes架构设计

SerDes 芯片因供应商而异,具体取决于它们的使用方式、所包含的通道数以及它们支持的速度等因素。即便如此,芯片制造商也倾向于在其 SerDes 设计中采用以下四种架构之一:

并行时钟(Parallel clock)

SerDes 将数据地址和控制信号与并行数据输入一起嵌入。串行流输出时会附带一个附加时钟信号,用于对数据进行反序列化。

嵌入式时钟(Embedded clock)

SerDes 将并行数据输入和参考时钟信号嵌入到单个串行流中。每个周期都会将两个时钟位嵌入到流中,以在每个位流周围创建一个帧。

8b/10b(8b/10b)

SerDes 将并行数据输入中的每个字节转换为 10 位符号(8 位加 2 位),并将符号嵌入到串行流中。编码方案通过限制连续 0 或 1 的数量差异来实现串行传输通道中的直流平衡。

位交织(Bit interleaved)

SerDes 通过交织来自输入流的位,将几个较慢的串行流复用为一个更快的流。

SerDes 芯片用于千兆以太网系统、无线网络路由器、光纤通信系统、存储系统、汽车部件和各种其他环境。当今许多 SerDes 设备的运行速度都超过 100 Gbps,而且更快的速度即将到来。

暂无评论内容